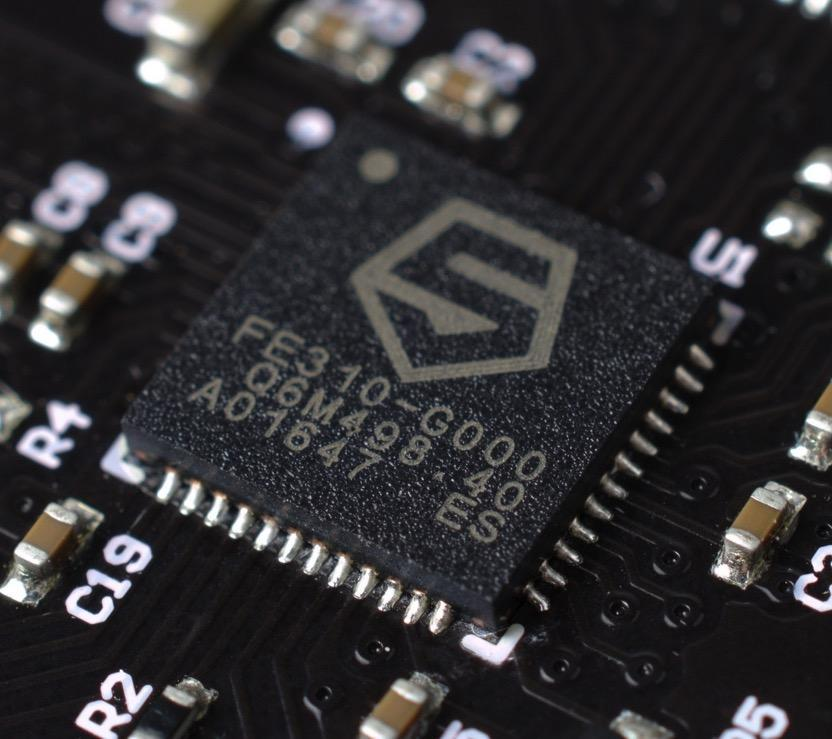

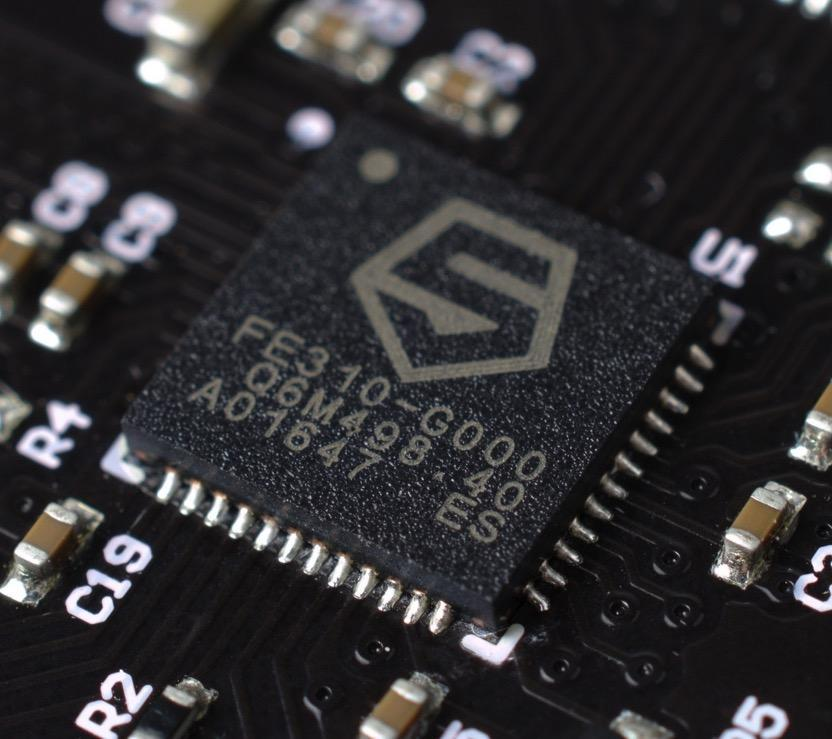

The 2019 Hackaday Superconference kicked off with a marvelous, and marvelously geeky, keynote talk on the subject of RISC-V by Dr. Megan Wachs.

from Pocket

via Did you enjoy this article? Then read the full version from the author’s website.

The 2019 Hackaday Superconference kicked off with a marvelous, and marvelously geeky, keynote talk on the subject of RISC-V by Dr. Megan Wachs.

from Pocket

via Did you enjoy this article? Then read the full version from the author’s website.

Finally a big dream of mine has come true. I built my own retro arcade cabinet! The whole parts cost about 700 euros. Since I am only a hobby craftsman and only have simple devices, it took a long time to set it up (3 Month in total). I gained some experience in woodworking.

from Pocket

via Did you enjoy this article? Then read the full version from the author’s website.

We recently obtained a clock that flew on a Soyuz space mission.1 The clock, manufactured in 1984, contains over 100 integrated circuits on ten circuit boards. Why is the clock so complicated? In this blog post, I examine the clock’s circuitry and explain why so many chips were needed.

from Pocket

via Did you enjoy this article? Then read the full version from the author’s website.

En début d’année 2019 se posait la question de savoir si ce serait l’année de la libération des FPGA. En ce début d’année 2020, essayons de faire un bilan. FPGA, ASC, HDL, RISC‑Ⅴ et PCB sont les chapitres que nous allons découvrir dans la suite de cet article.

from Pocket

via Did you enjoy this article? Then read the full version from the author’s website.

RISC-V Educational Materials Author/University Link Access Level Platform Content Type Udemy Link Paid 2 Sim HW a,d Oakland University Link Open 2 Unspecified HW f University of Rochester Link Open 1 Unspecified SW f University of Cambridge Link Open 2 FPGA HW f University of Wisconsin-Madison Link

from Pocket

via Did you enjoy this article? Then read the full version from the author’s website.

RSD is a 32-bit RISC-V out-of-order superscalar processor core. RSD is very fast due to aggressive OoO features, while it is very compact and can be synthesized for small FPGAs. The key features of RSD are as follows: Install the following software for running simulation.

from Pocket

via Did you enjoy this article? Then read the full version from the author’s website.

When we make a telephone call in 2020 it is most likely to be made using a smartphone over a cellular or IP-based connection rather than a traditional instrument on a pair of copper wires to an exchange.

from Pocket

via Did you enjoy this article? Then read the full version from the author’s website.

I recently found some USB devices on eBay (Epiphan VGA2USB LR) that could take VGA as input and present the output as a webcam.

from Pocket

via Did you enjoy this article? Then read the full version from the author’s website.