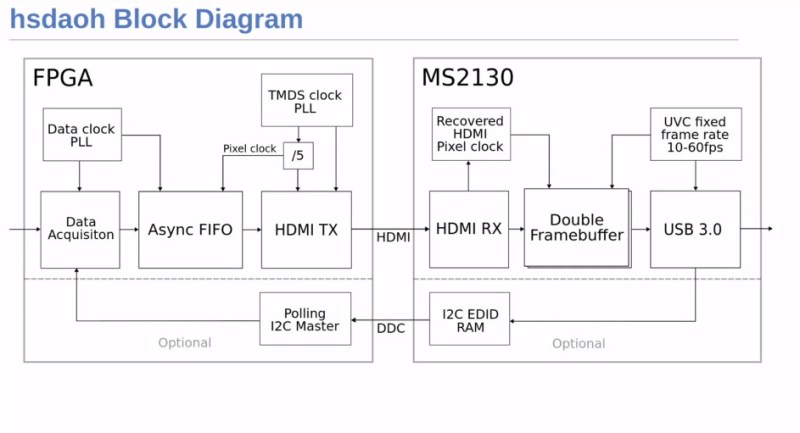

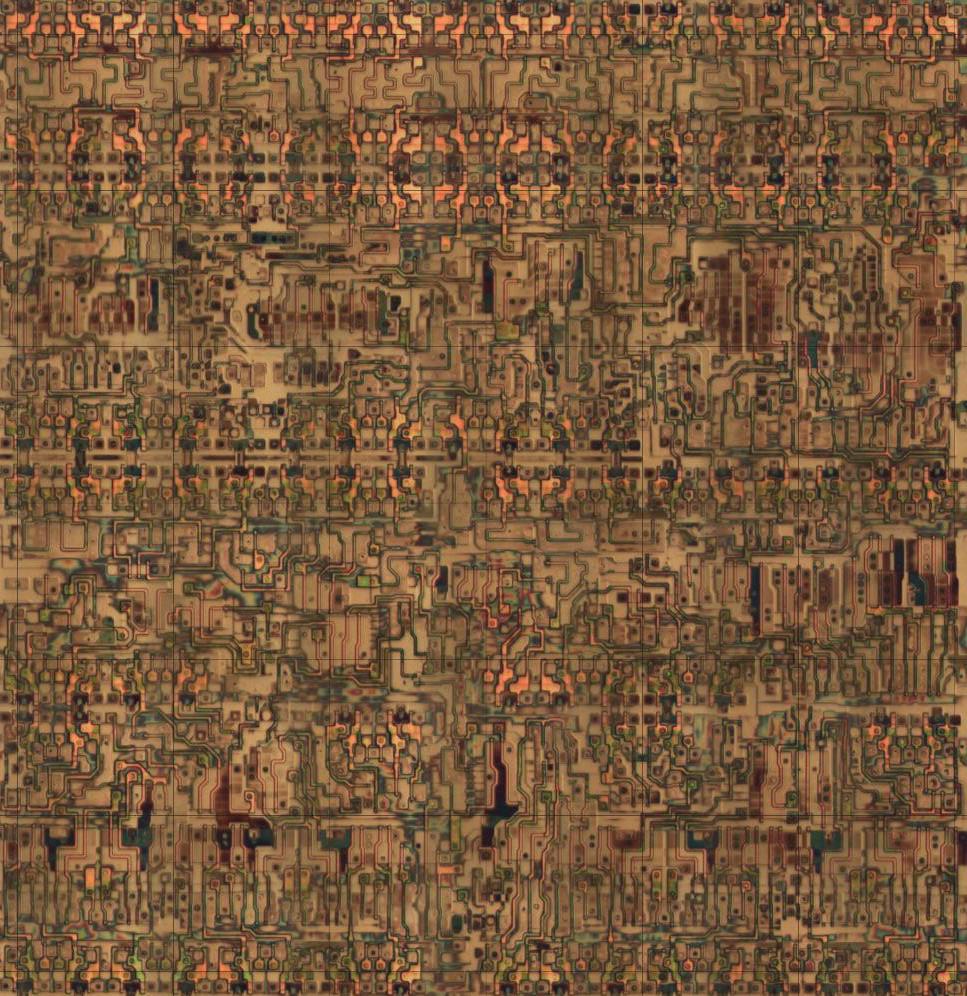

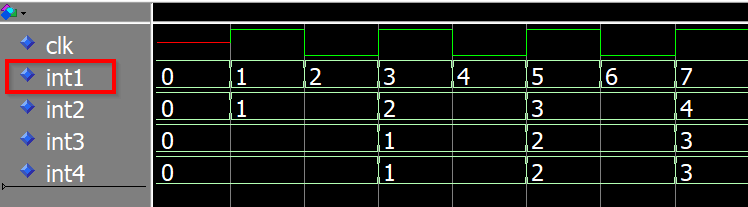

Let’s say you had a SNES with a busted CPU. What would you do? Your SNES would be through! That is, unless, you had a replacement based on an FPGA. [leonllr] has been developing just such a thing. The project was spawned out of necessity.

from Pocket

via Did you enjoy this article? Then read the full version from the author’s website.